# Utilizing Signal Temporal Logic to Characterize and Compose Modules in Synthetic Biology

Curtis Madsen, Prashant Vaidyanathan, Cristian-Ioan Vasile, Rachael Ivison, Junmin Wang, Calin Belta, and Douglas Densmore

#### **Introduction**

- One of the fundamental goals in the field of synthetic biology is to reliably engineer biological systems to respond to environmental conditions according to a pre-determined genetic program.

- Using Boolean logic functions, synthetic biologists have successfully engineered living cells to perform certain functions<sup>1</sup>.

- However, it has been difficult to realize the full potential of genetically encoded logic in practical applications without the ability to specify timing and performance of genetic circuits.

<sup>1</sup>A. A. Nielsen, B. S. Der, J. Shin, P. Vaidyanathan, V. Paralanov, E. A. Strychalski, D. Ross, D. Densmore, and C. A. Voigt, "Genetic circuit design automation," Science.

## **Performance Specifications**

- To remedy this issue, we propose using performance specifications.

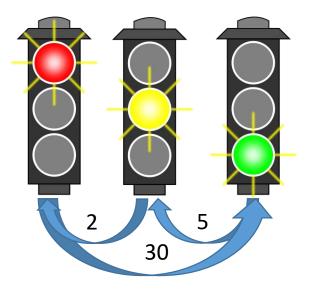

- For example, we can give a performance specification for a traffic light:

- A traffic light should remain green *until* a pedestrian requests a walk signal. *Within 5 seconds* of receiving the request, the traffic light should change to yellow for *2 seconds*, and then change to red for *30 seconds* before switching back to green.

## **Performance Specifications**

- Temporal logic can be used to write performance specifications as it allows for reasoning about behavior over time.

- In particular, we use Signal Temporal Logic (STL) as it allows for the specification of requirements on signals at specific times leading to a level of expressiveness necessary for genetic circuit design.

## **Temporal Logic Syntax**

- Logical Operators:

- Conjunction:  $\phi \land \psi$

- Disjunction:  $\phi \lor \psi$

- Implication:  $\phi \rightarrow \psi$

- Negation: ¬φ

- Temporal Operators:

- Until:  $\phi \cup \psi$

- Future (Eventually): F  $\phi$  (or  $\Diamond \phi$ )

- Globally: G  $\phi$  (or  $\Box \phi$ )

## Until Operator

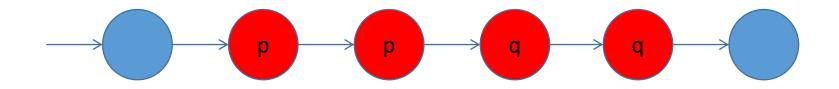

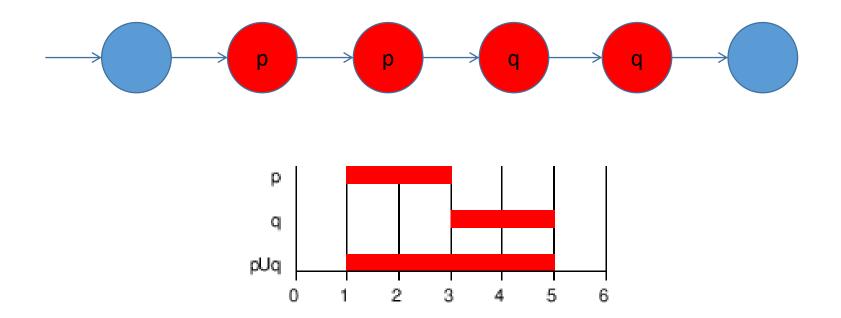

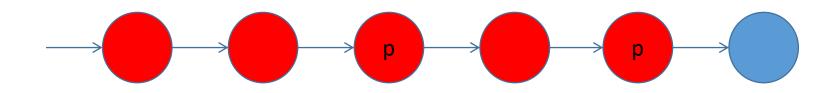

рUq

• q holds at the current or a future position, and p has to hold until that position. At that position p does not have to hold any more.

## <u>Until Operator</u>

рUq

• q holds at the current or a future position, and p has to hold until that position. At that position p does not have to hold any more.

## Until Operator

рUq

• q holds at the current or a future position, and p has to hold until that position. At that position p does not have to hold any more.

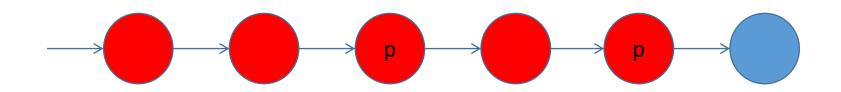

# Future (Eventually) Operator

Fр

• Future: p eventually has to hold (somewhere on the subsequent path).

## Future (Eventually) Operator

Fр

• Future: p eventually has to hold (somewhere on the subsequent path).

## Future (Eventually) Operator

Fр

• Future: p eventually has to hold (somewhere on the subsequent path).

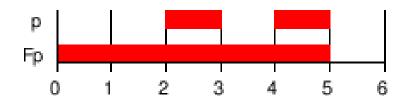

## **Globally Operator**

Gр

• Globally: p has to hold on the entire subsequent path.

## **Globally Operator**

Gр

• Globally: p has to hold on the entire subsequent path.

## **Globally Operator**

Gр

• Globally: p has to hold on the entire subsequent path.

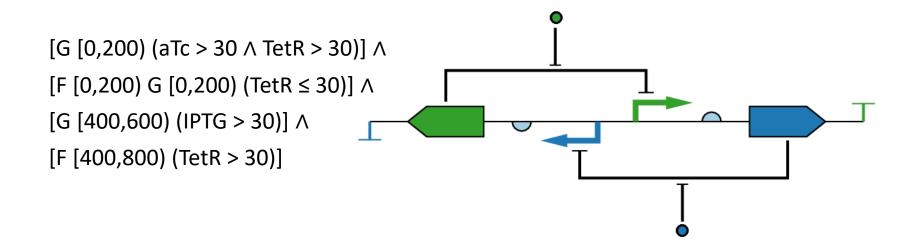

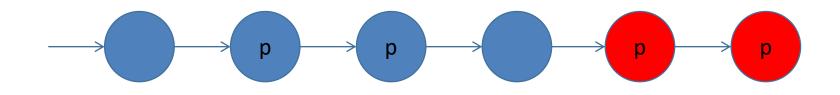

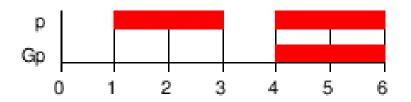

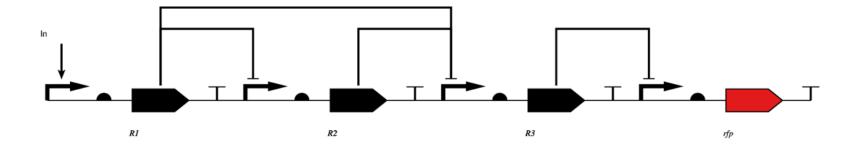

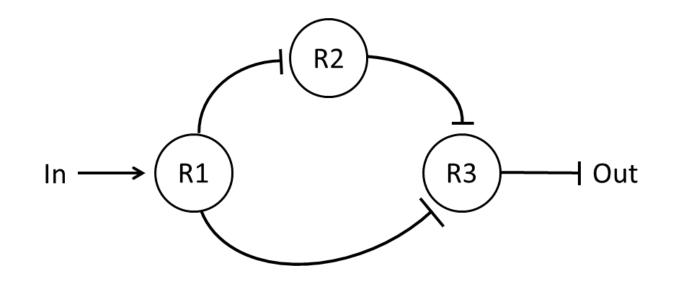

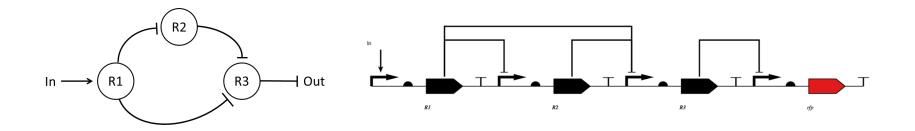

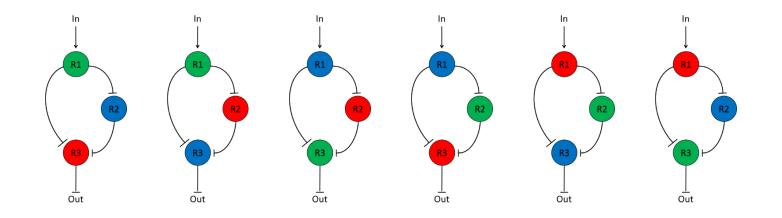

#### <u>Repressor Incoherent FeedForward Loop (RIFFL)</u>

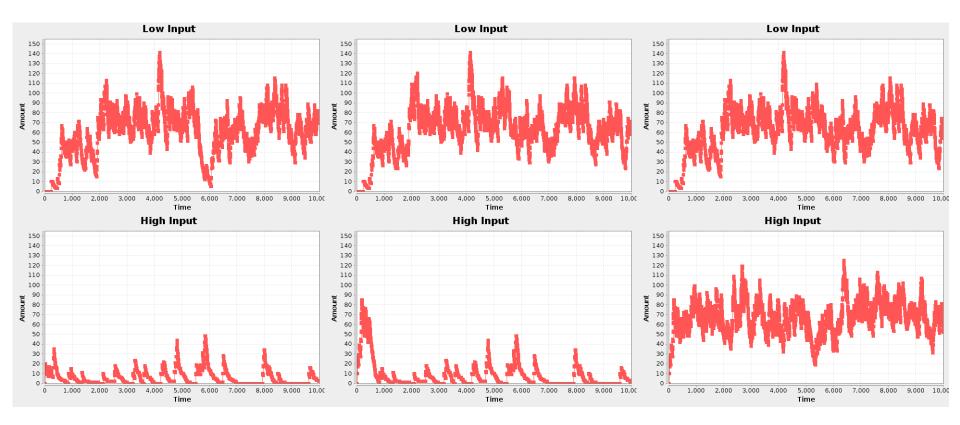

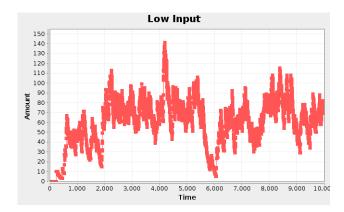

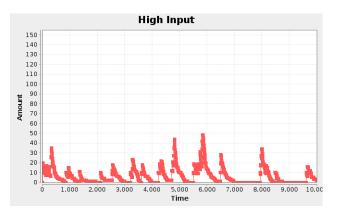

#### **Potential Behaviors**

• Depending on which repressor modules are used, different behaviors can be achieved.

# Signal Temporal Logic (STL)

- These behaviors must be encoded in STL.

- For instance, when "In" is greater than 100, "Out" always eventually rises above 50 within 1000 time units.

- Also, when "In" is 0, "Out" always remains below 50.

This corresponds to the following STL:

[G [0,10000) (In > 100)] → [G [0,10000) F [0,1000) (Out > 50)] ∧

[G [0,10000) (In ≤ 0)] → [G [0,10000) (Out ≤ 50)]

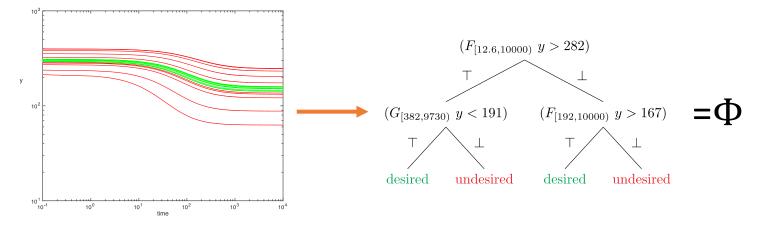

## <u>Characterization – Temporal Logic Inference (TLI)</u>

- Using supervised learning, TLI<sup>2</sup> can be used to "learn" an STL formula from time series data.

- The current implementation of TLI works by finding optimal STL primitives and parameters:

- $G_{[t_0,t_1]} x_i < k$ ,  $F_{[t_0,t_1]} x_i > k$ ,

- $G_{[t_0,t_1]} x_i > k$ ,  $F_{[t_0,t_1]} x_i < k$ , ...

- $t_0, t_1, k$  found by simulated annealing

<sup>2</sup>G. Bombara, C.-I. Vasile, F. Penedo, H. Yasuoka, and C. Belta, "A Decision Tree Approach to Data Classification using Signal Temporal Logic," presented at the Proceedings of the 19th International Conference on Hybrid systems: Computation and Control, New York, NY, USA, 2016, pp. 1–10.

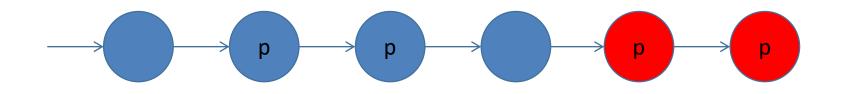

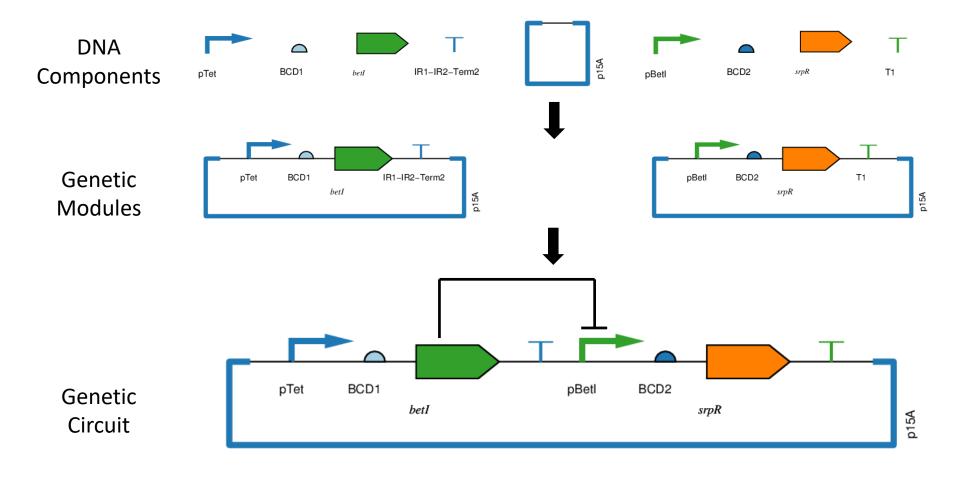

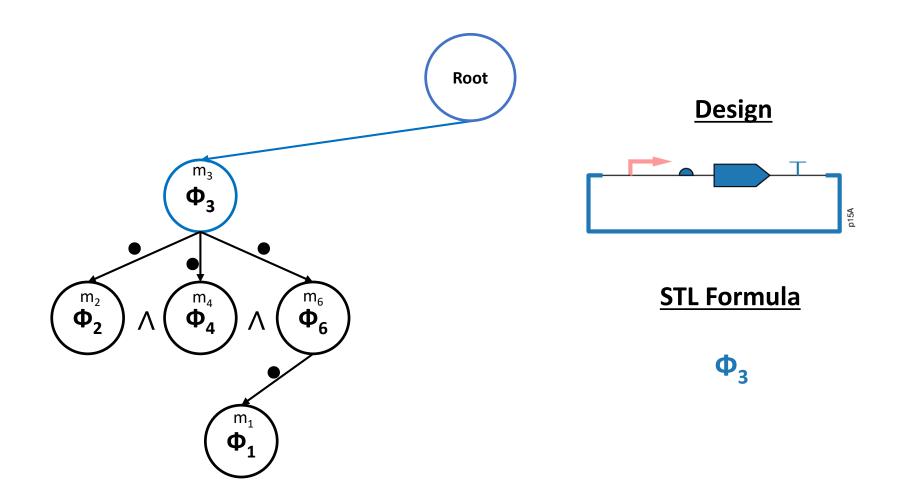

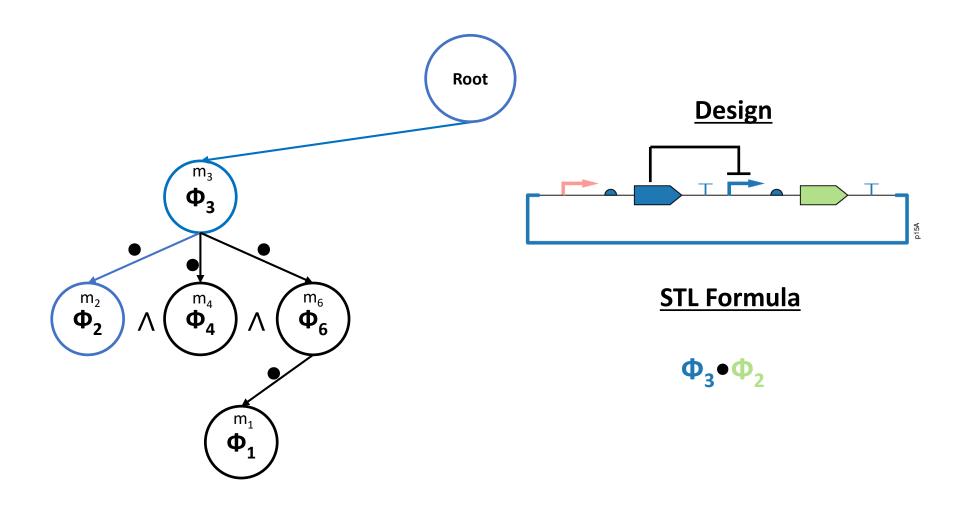

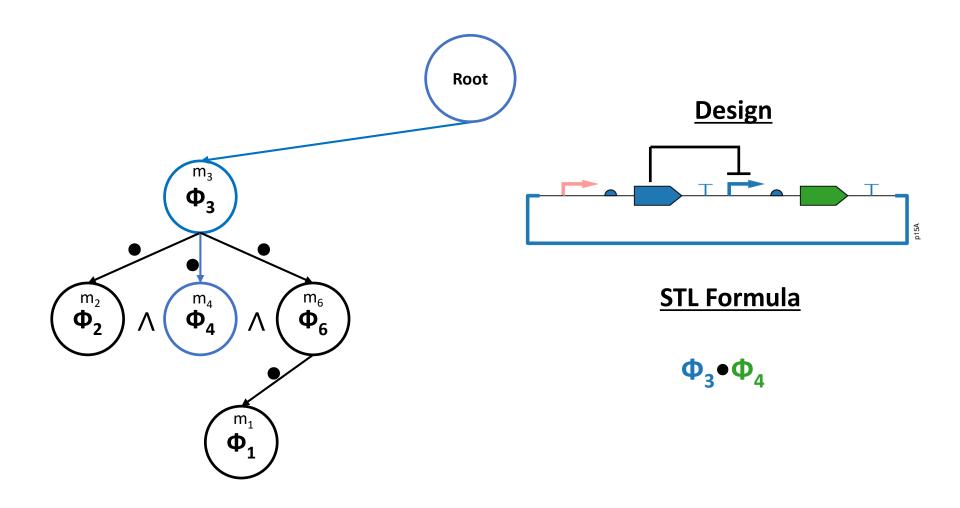

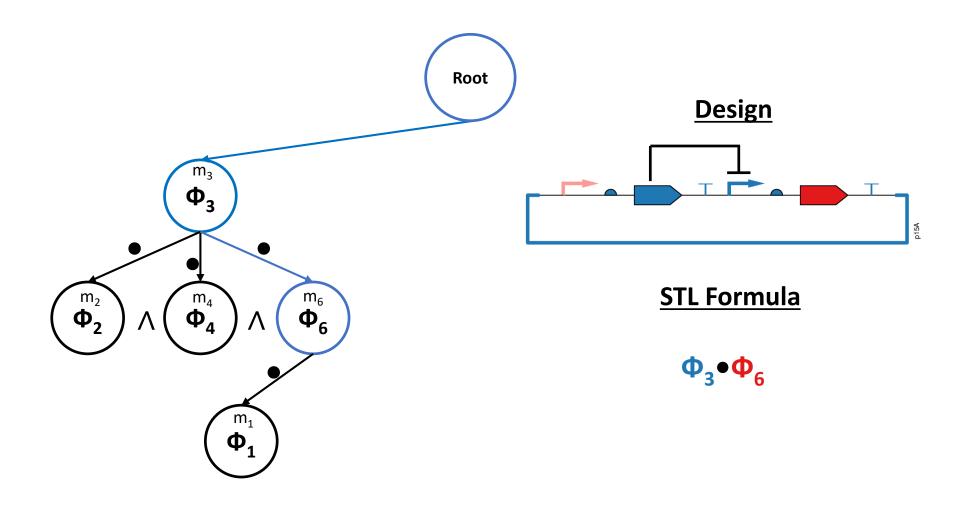

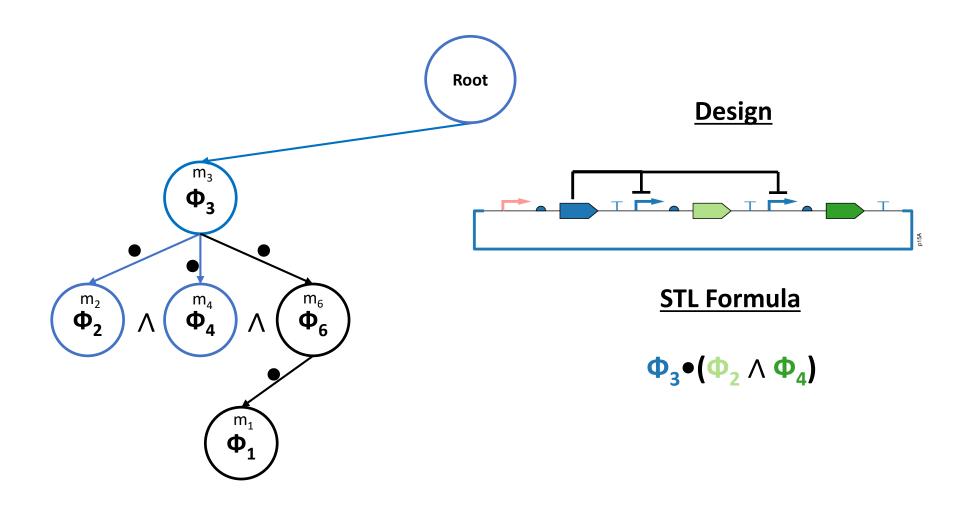

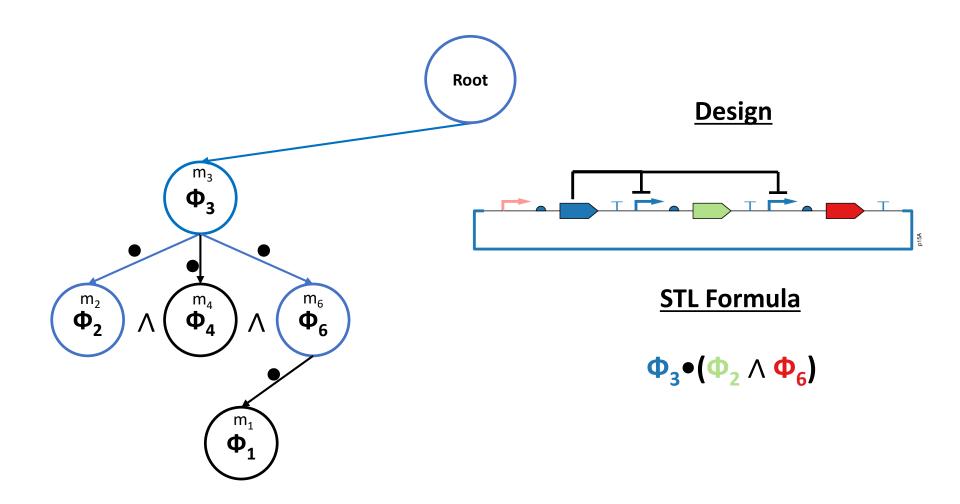

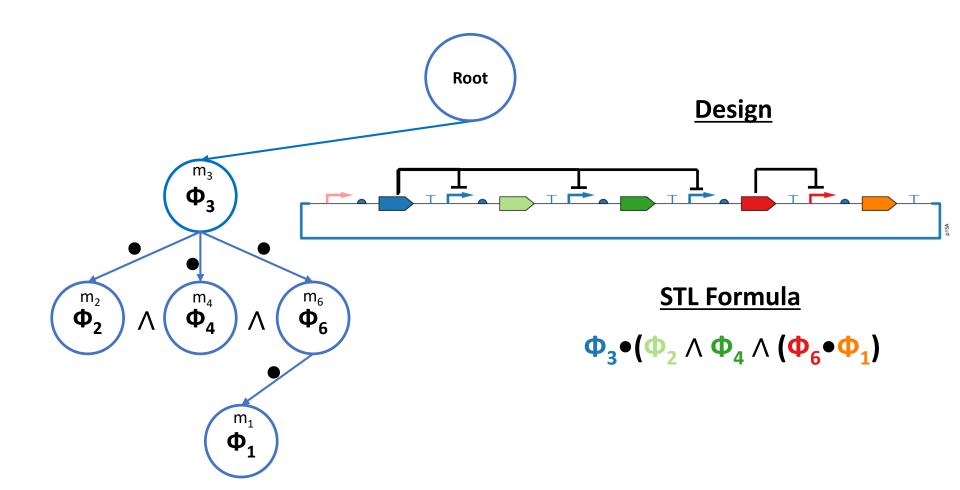

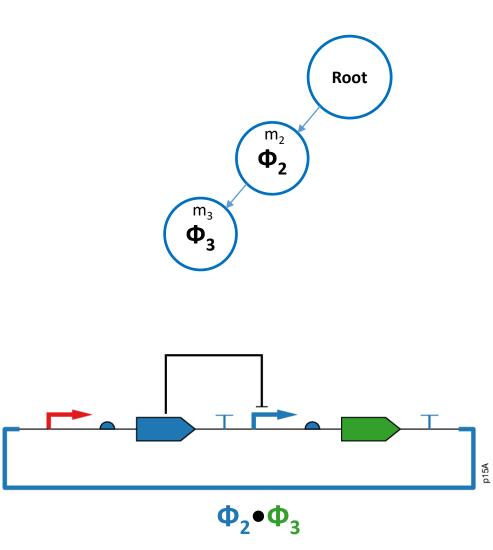

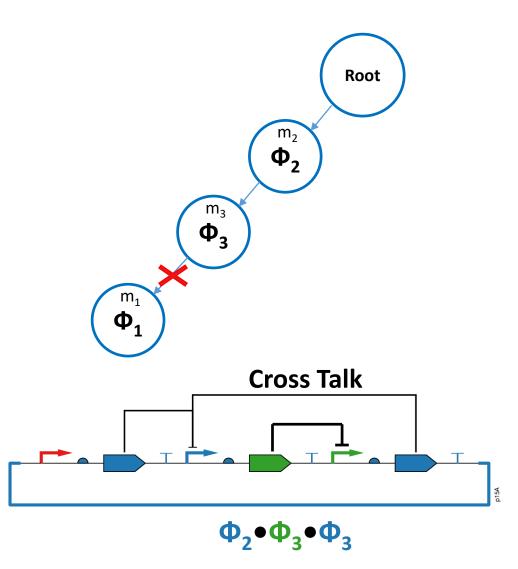

## **Composability in Synthetic Biology**

• DNA segments representing genetic parts and modules can be composed to create genetic circuits.

- STL with added functionality:

- Concatenation (•) allows one STL formula to connect to another in sequence.

- Inputs signals that are annotated as drivers of the formula.

- Outputs signals that are annotated as being produced by the formula.

- Mapping a collection of assignments among the inputs and outputs of STL formulae.

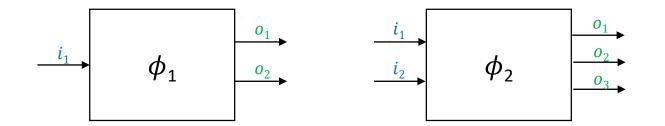

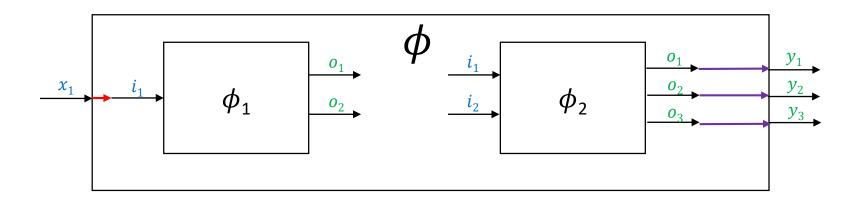

- For instance,  $\phi$  is composed of  $\phi_1$  and  $\phi_2$ :

- STL with added functionality:

- Concatenation (•) allows one STL formula to connect to another in sequence.

- Inputs signals that are annotated as drivers of the formula.

- Outputs signals that are annotated as being produced by the formula.

- Mapping a collection of assignments among the inputs and outputs of STL formulae.

- For instance,  $\phi$  is composed of  $\phi_1$  and  $\phi_2$ :

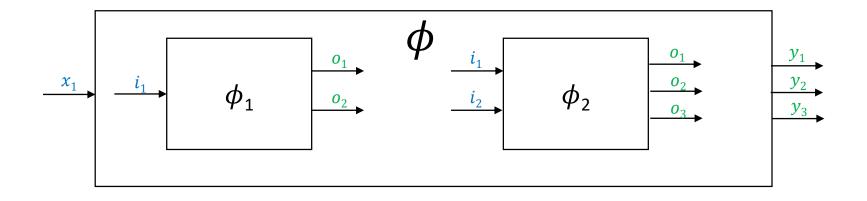

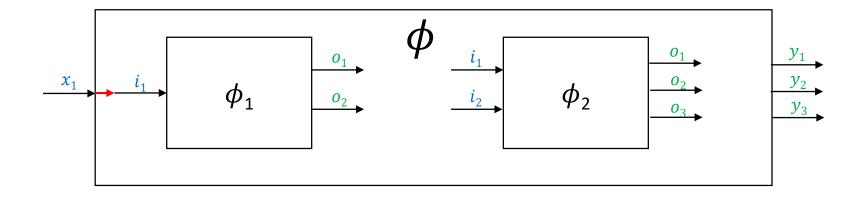

- Concatenation  $\phi(x_1, y_1, y_2, y_3) = \phi_1(i_1, o_1, o_2) \bullet \phi_2(i_1, i_2, o_1, o_2, o_3).$

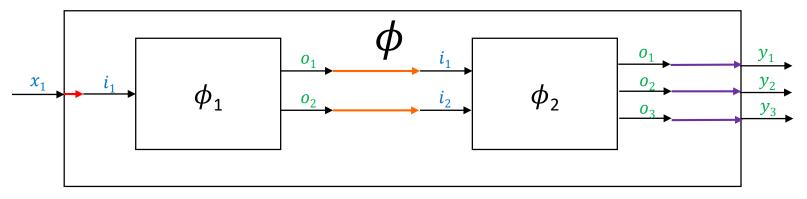

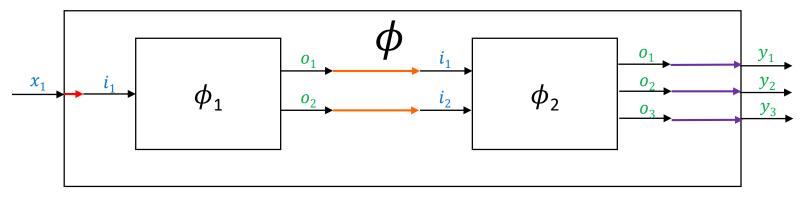

- STL with added functionality:

- Concatenation (•) allows one STL formula to connect to another in sequence.

- Inputs signals that are annotated as drivers of the formula.

- Outputs signals that are annotated as being produced by the formula.

- Mapping a collection of assignments among the inputs and outputs of STL formulae.

- For instance,  $\phi$  is composed of  $\phi_1$  and  $\phi_2$ :

- Concatenation  $-\phi(x_1, y_1, y_2, y_3) = \phi_1(i_1, o_1, o_2) \bullet \phi_2(i_1, i_2, o_1, o_2, o_3).$

- Input mapping  $(\phi: x_1 = \phi_1: i_1)$ .

- STL with added functionality:

- Concatenation (•) allows one STL formula to connect to another in sequence.

- Inputs signals that are annotated as drivers of the formula.

- Outputs signals that are annotated as being produced by the formula.

- Mapping a collection of assignments among the inputs and outputs of STL formulae.

- For instance,  $\phi$  is composed of  $\phi_1$  and  $\phi_2$ :

- Concatenation  $-\phi(x_1, y_1, y_2, y_3) = \phi_1(i_1, o_1, o_2) \bullet \phi_2(i_1, i_2, o_1, o_2, o_3).$

- Input mapping  $(\phi: x_1 = \phi_1: i_1)$ .

- Output mapping  $(\phi: y_1 = \phi_2: o_1) \land (\phi: y_2 = \phi_2: o_2) \land (\phi: y_3 = \phi_2: o_3).$

- STL with added functionality:

- Concatenation (•) allows one STL formula to connect to another in sequence.

- Inputs signals that are annotated as drivers of the formula.

- Outputs signals that are annotated as being produced by the formula.

- Mapping a collection of assignments among the inputs and outputs of STL formulae.

- For instance,  $\phi$  is composed of  $\phi_1$  and  $\phi_2$ :

- Concatenation  $\phi(x_1, y_1, y_2, y_3) = \phi_1(i_1, o_1, o_2) \bullet \phi_2(i_1, i_2, o_1, o_2, o_3).$

- Input mapping  $(\phi: x_1 = \phi_1: i_1)$ .

- Output mapping  $(\phi: y_1 = \phi_2: o_1) \land (\phi: y_2 = \phi_2: o_2) \land (\phi: y_3 = \phi_2: o_3).$

- Internal mapping  $(\phi_1: o_1 = \phi_2: i_1) \land (\phi_1: o_2 = \phi_2: i_2)$ .

- STL with added functionality:

- Concatenation (•) allows one STL formula to connect to another in sequence.

- Inputs signals that are annotated as drivers of the formula.

- Outputs signals that are annotated as being produced by the formula.

- Mapping a collection of assignments among the inputs and outputs of STL formulae.

- For instance,  $\phi$  is composed of  $\phi_1$  and  $\phi_2$ :

- Concatenation  $\phi(x_1, y_1, y_2, y_3) = \phi_1(i_1, o_1, o_2) \bullet \phi_2(i_1, i_2, o_1, o_2, o_3).$

- Input mapping  $(\phi: x_1 = \phi_1: i_1)$ .

- Output mapping  $(\phi: y_1 = \phi_2: o_1) \land (\phi: y_2 = \phi_2: o_2) \land (\phi: y_3 = \phi_2: o_3).$

- Internal mapping  $(\phi_1: o_1 = \phi_2: i_1) \land (\phi_1: o_2 = \phi_2: i_2)$ .

Note: The mapping can be applied to other STL operators, not just concatenation.

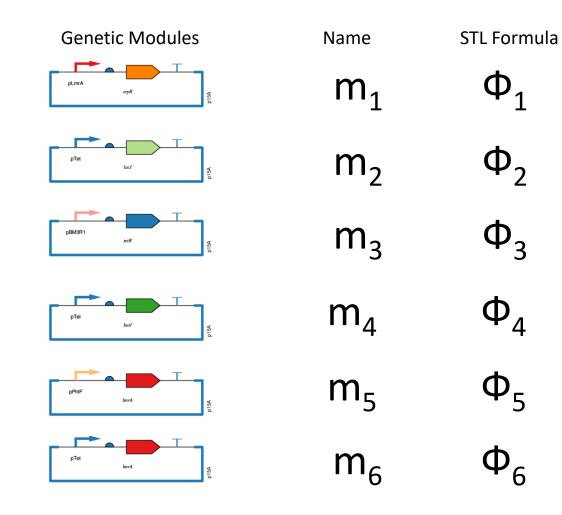

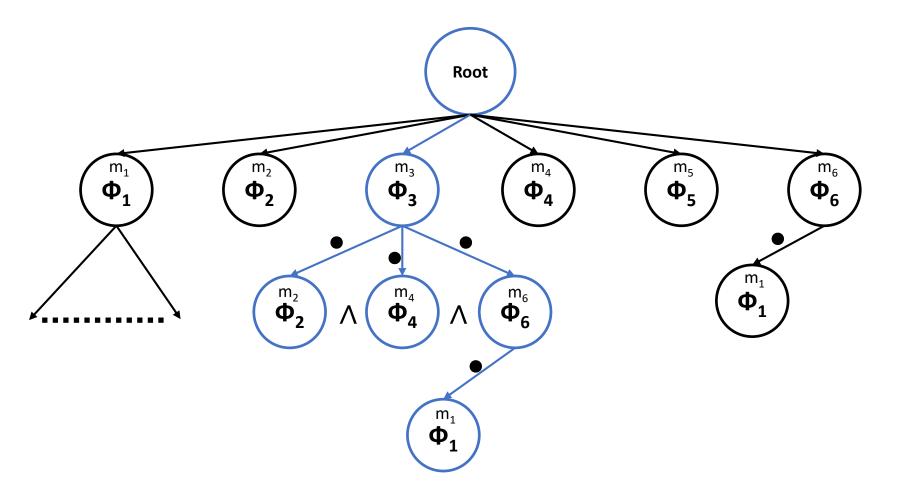

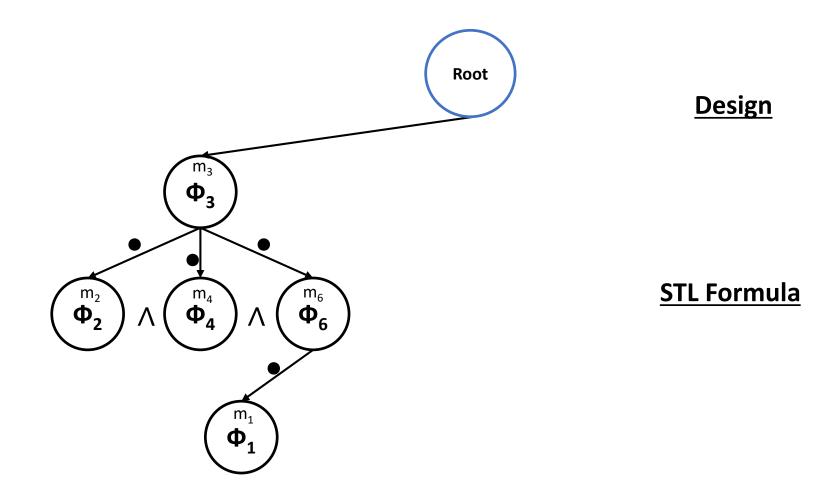

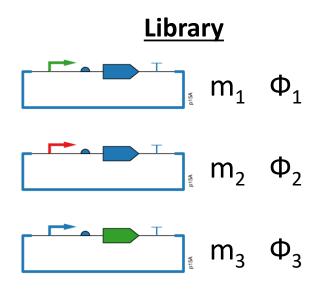

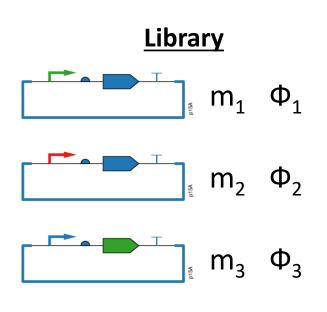

## **Library**

## **Constraint Pruning**

## **Constraint Pruning**

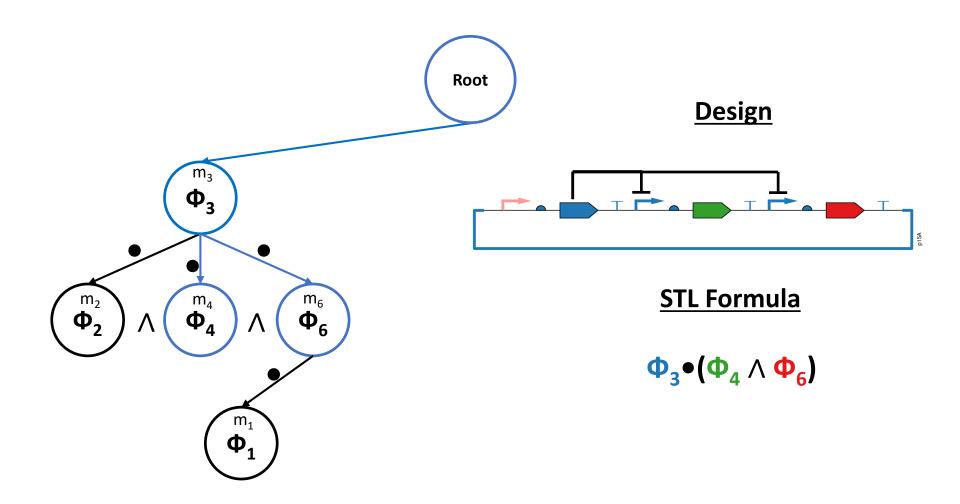

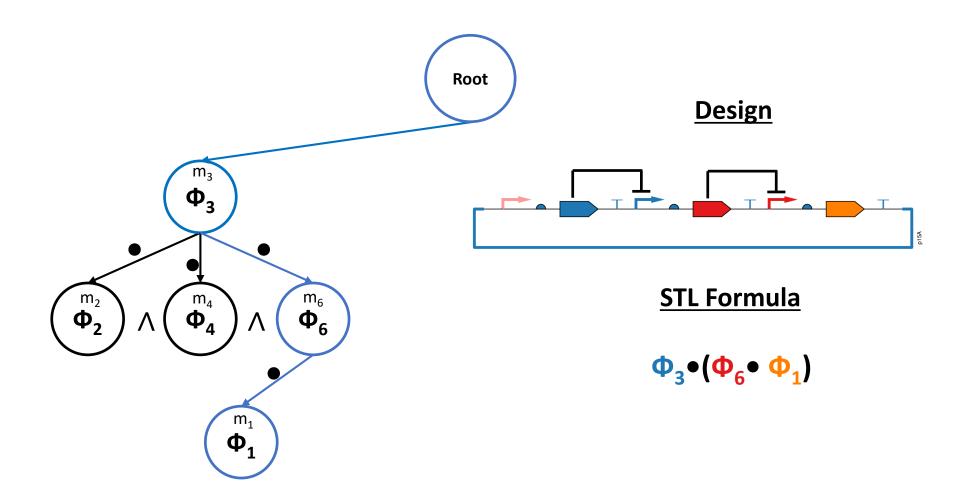

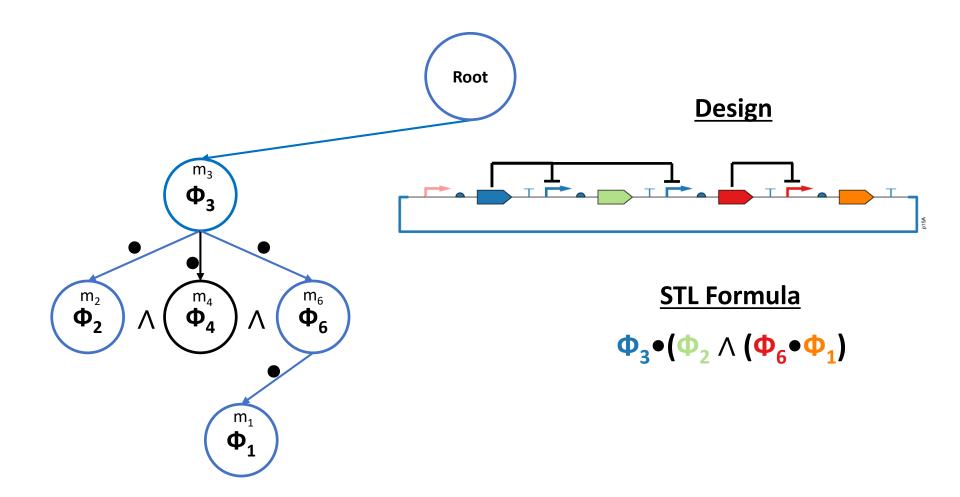

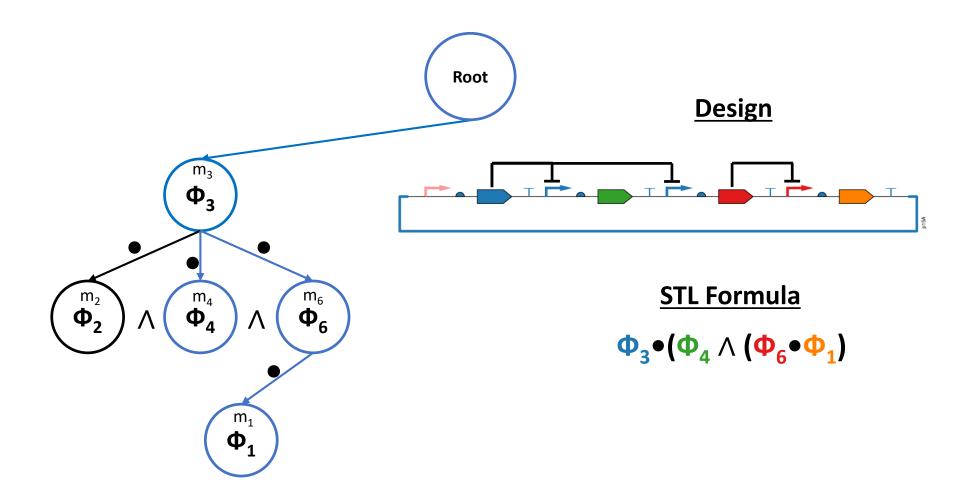

#### Possible RIFFL Circuit Designs

## Future Work

- Currently, TLI requires both desirable and undesirable traces.

- We are working on a method that only requires desirable traces.

- We are adding constraints to help prune the potential design space of the composed genetic circuits.

- We are currently testing these methods on mammalian and bacterial synthetic biology examples.

## **Acknowledgements**

Prashant Vaidyanathan

Cristian-Ioan Vasile

**Rachael Ivison**

Junmin Wang

Calin Belta

**Douglas Densmore**

This work is supported by the National Science Foundation under grant CPS Frontier 1446607.