# MINT - Microfluidic Netlist Radhakrishna Sanka, Haiyao Huang, Ryan Silva and Douglas Densmore Boston University, Boston, Massachusetts, USA

## Introduction

The major advaces in electronics can be attributed to the advances in CAD tools. MINT is the first step in trying to replicate the versatile toolkit available to elec tronics designers. With MINT, microfluidics designers can easily create large and complex microfluidics designs. This can be done using the ever increasing librai of various components like cell traps, valves, ports, mul tiplexers, mixers, and even transposers that are being added to MINT.

## Why MINT?

### Standard Design Toolkit

Since all of the components in MINT are derived from existing academic literature, a standard design toolkit would ensure that all the designs would work as expected within predefined operational tolerances.

### **Portability Between CAD Tools**

By sticking to a standard specificaiton interface we can ensure that the Microfluidic Designs can be used by di ferent tools during the various phases of the design process. This versatility enables horizontal integration amongst tools and sets precedence for an industry wide standardization. MINT is fully supported by Fluigi

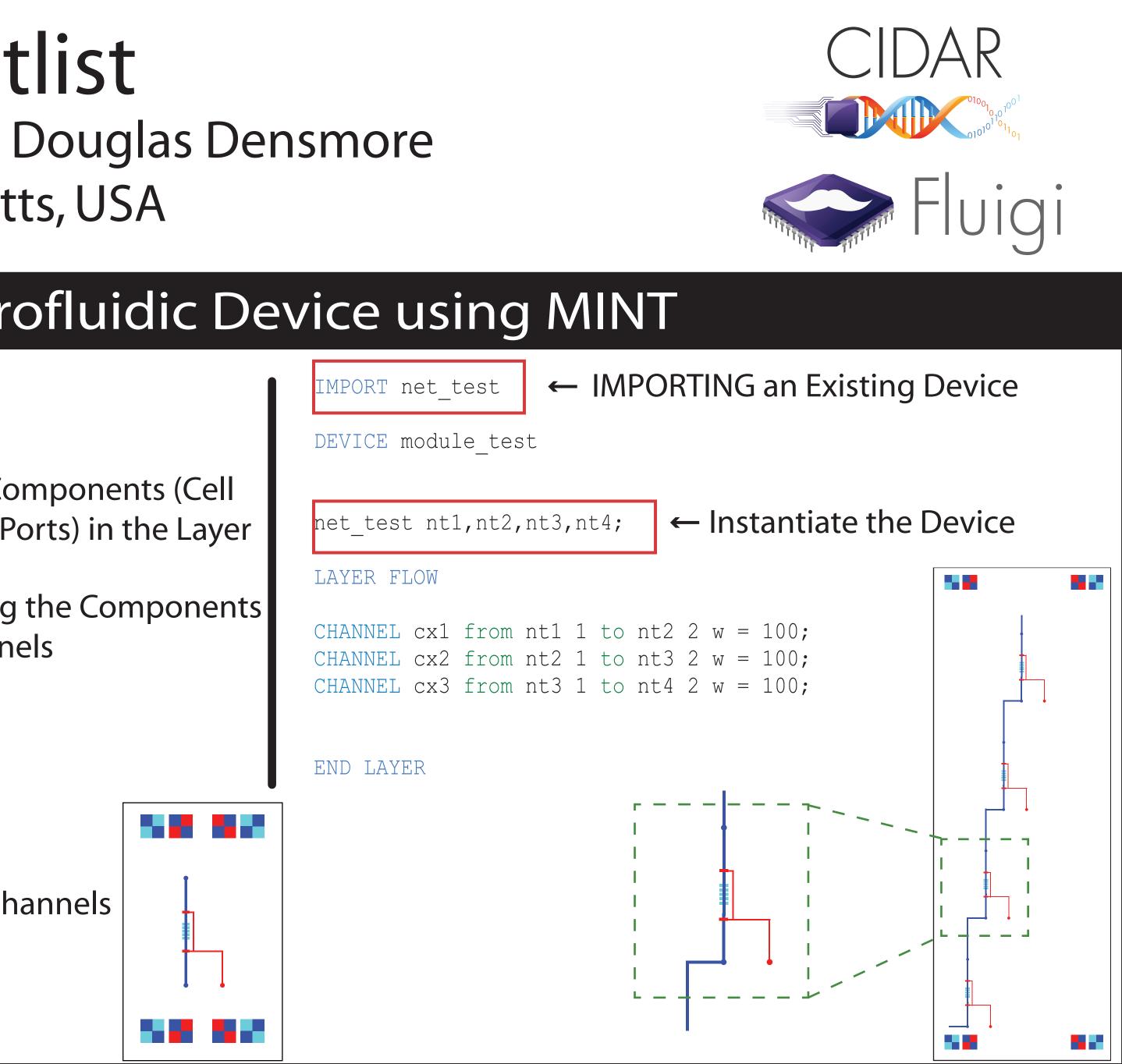

### **Embedded and Reusable Designs**

MINT allows researchers and designers to specify their designs in a format that is human readable and easily shared in the form of a text file. In addition to this functionality, the user can also create and import existing design libraries into thier own library.

|          | Defining a Microfluidic D                                                                                                                                                                                                                                                                                                                                        | Device using MINT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | DEVICE net_test ← Declaring a Device<br>LAYER FLOW ← Defining the Flow Layer<br>PORT p1, p2 r=100;<br>V LONG CELL TRAP ct1 numChambers=10<br>chamberWidth=100 chamberLength=100<br>chamberSpacing=50 channelWidth=100;                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ry<br>I- | CHANNEL c1 from p1 3 to ct1 1 w=100;<br>CHANNEL c2 from ct1 2 to p2 1 w=100;<br>TERMINAL 1 p1;<br>TERMINAL 2 p2;<br>END LAYER ← Defining the End of the Layer<br>LAYER CONTROL ← Defining the Control Layer<br>PORT p3 r=100;<br>VALVE v1 on c1 w=300 1=100;<br>VALVE v2 on c2 w=300 1=100;<br>NET net1 from p3 1 to v1 4, v2 4<br>channelWidth=50;<br>END LAYER | <pre>CHANNEL cx1 from nt1 1 to nt2 2 w = 100;<br/>CHANNEL cx2 from nt2 1 to nt3 2 w = 100;<br/>CHANNEL cx3 from nt3 1 to nt4 2 w = 100;<br/>END LAYER</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

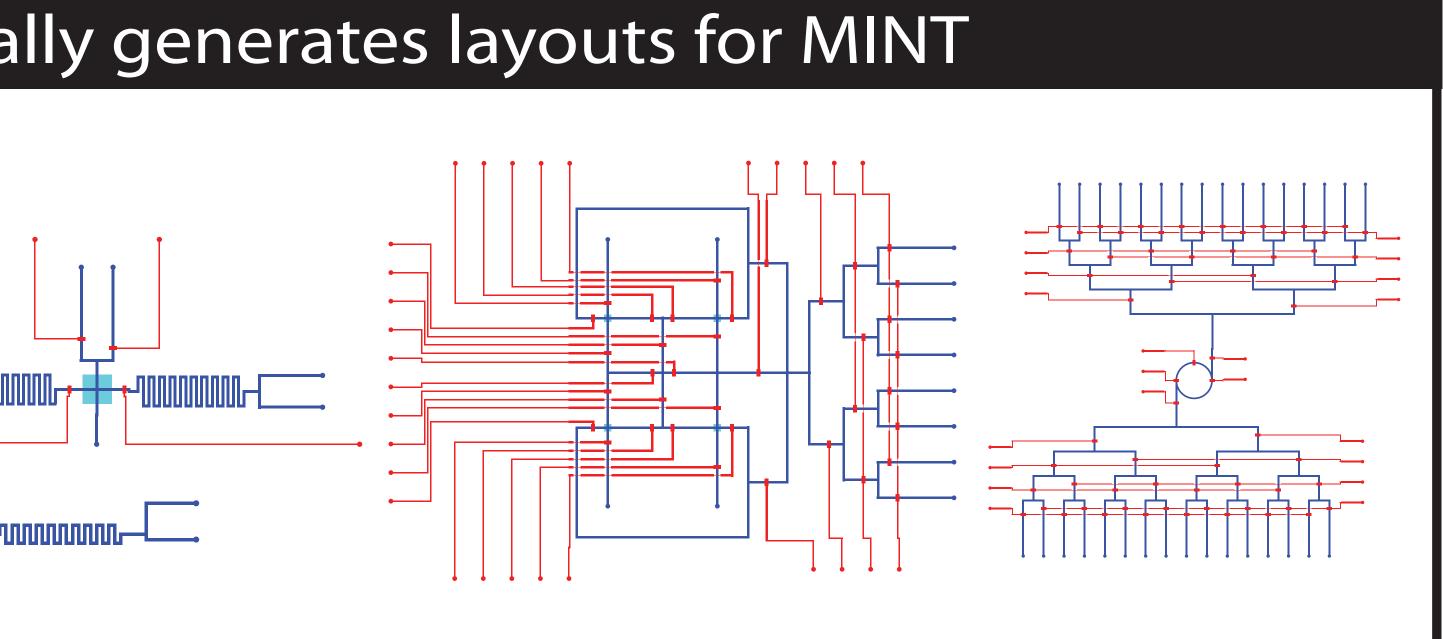

| n<br>if- | Fluigi – Automatically generation                                                                                                                                                                                                                                                                                                                                | ates layouts for MINT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|          | CELL TRAP<br>MIXER<br>MUX<br>GRADIENT GEN-<br>ERATOR<br>MUX<br>TRANSPOSER<br>ROTARY<br>DROPLET                                                                                                                                                                                                                                                                   | <ul> <li>References</li> <li>MINT Github Wiki. https://github.com/CIDARLAB/mint/wiki, 2016.</li> <li>V. Betz and J. Rose. VPR: A new packing, placement, and routing tool for FPGA rese</li> <li>S. K. W. Dertinger, D. T. Chiu, N. L. Jeon, and G. M. Whitesides. Generation of Gradie<br/>ex Shapes Using Microuidic Networks.</li> <li>M. S. Ferry, I. A. Razinkov, and J. Hasty. Chapter fourteen - Microfuidics for Synthetic<br/>esign to Execution.</li> <li>F. Hadlock. A shortest path algorithm for grid graphs Networks.</li> <li>H. Huang. Fluigi: An end-to-end Software Work Flowvfor Microfluidic Design. PhD the<br/>rsity, 2015.</li> <li>H. Huang and D. Densmore. Fluigi: Microfluidic device synthesis for synthetic biology<br/>A. A. K. Nielsen, B. S. Der, J. Shin, P. Vaidyanathan, V. Paralanov, E. A. Strychalski, D.<br/>ore and C. A. Voigt. Genetic circuit design automation.</li> <li>A. Prindle, P. Samayoa, I. Razinkov, T. Danino, L. S.Tsimring, and J. Hasty. A sensing<br/>upled genetic / biopixels/.</li> <li>B. Silva, A. Heuckroth, C. Huang, A. Rolfe, and D. Densmore. Makerfuidics: Microfu<br/>17. M. Squires and S. R. Quake. Microfuidics: Fluid physics at the nanoliter scale.</li> <li>T. Thorsen, S. J. Maerkl, and S. R. Quake. Microfuidic Large-Scale Integration.</li> <li>J. P. Urbanski, W. Thies, C. Rhodes, S. Amarasinghe, and T. Thorsen. Digital microfu<br/>for graphy.</li> </ul> |